# Построение входных и выходных цепей

## программируемых аналоговых схем Anadigm

Программируемые аналоговые микросхемы Anadigm второго поколения серии AnadigmVortex работают с однополярными дифференциальными сигналами в диапазоне напряжений от 0 до +4,0 В с постоянной составляющей +2,0 В. В статье приведены схемы сопряжения ПАИС Anadigm для однополярных и биполярных сигналов и/или амплитудой входных сигналов, выходящих за пределы максимально допустимых уровней, а также описываются методы работы с недифференциальными сигналами.

Александр ЩЕРБА shcherba@prosoft.ru

### Структура программируемых аналоговых микросхем Anadigm

Лидером в разработке и производстве программируемых аналоговых микросхем (ПАИС) является компания Anadigm. ПАИС разделяются на динамически и статически

конфигурируемые. В отличие от статически программируемых схем, где конфигурационные данные загружаются при включении ПАИС и остаются неизменными во время ее работы, динамически конфигурируемая схема позволяет изменять полностью или частично функциональную структуру в реаль-

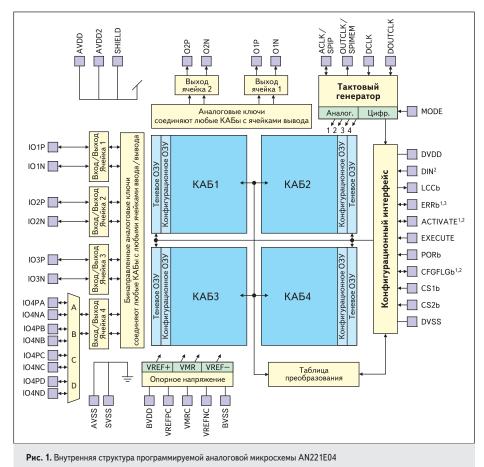

ном времени в работающем устройстве, что дает возможность создавать уникальные схемы аналоговой обработки сигналов. На рис. 1 представлена внутренняя структура программируемой аналоговой микросхемы Anadigm второго поколения.

Основу ПАИС составляют конфигурируемые аналоговые блоки (КАБ), которые содержат наборы элементов для реализации стандартных устройств — усилителей, фильтров, компараторов, источников образцового напряжения, АЦП [2]. Входные аналоговые сигналы подаются в КАБ через конфигурируемые двунаправленные ячейки ввода/вывода. Каждая ячейка ввода/вывода может осуществлять предварительную обработку сигнала с помощью набора стандартных устройств: буферный усилитель, усилитель с программируемым коэффициентом усиления, программируемый фильтр, прецизионный усилитель со стабилизацией прерыванием [1].

Синхронизация в ПАИС осуществляется с помощью внешнего или встроенного тактового генератора с внешним кварцевым резонатором. Частота внутреннего тактового генератора может быть поделена четырьмя синхронными программируемыми делителями, каждую из частот возможно вывести на внешний выход.

Режимы работы КАБ, значения тактовых частот, направления передачи сигналов, назначения и конфигурация ячеек ввода/вывода хранятся в конфигурационной памяти. Копия содержимого конфигурационной памяти хранится в теневом ОЗУ, которое может перезаписываться без нарушения процесса обработки сигнала. Это позволяет динамически изменять конфигурацию ПАИС в работающем устройстве во время работы. После загрузки в теневое ОЗУ новых данных

конфигурация устройства изменяется за один цикл тактовой синхронизации.

Все конфигурируемые аналоговые блоки имеют доступ к общей таблице преобразования, в которой хранится информация о передаточных характеристиках устройств, необходимых для реализации таких функций, как сжатие динамического диапазона, линеаризация сигналов датчиков, формирование сигналов произвольной формы, управляемая фильтрация.

Архитектура ПАИС включает в себя простой и гибкий конфигурационный интерфейс. После включения питания конфигурация из EPROM будет автоматически загружена, и ПАИС мгновенно начнет работать. Конфигурационный интерфейс выполняет функцию связи ПАИС с внешним микроконтроллером через SPI-порт, в режиме ведомого устройства. С его помощью можно динамически конфигурировать ПАИС и наращивать их количество для создания больших систем аналоговой обработки [3].

#### Построение входных цепей ПАИС

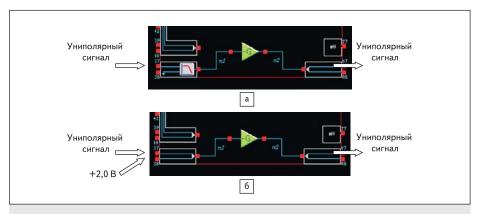

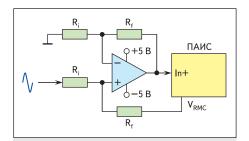

Обработка сигнала внутри ПАИС осуществляется с использованием однополярных дифференциальных сигналов, с постоянной составляющей +2,0 В. Для работы с недифференциальным униполярным аналоговым сигналом предусмотрена работа входной ячейки ПАИС в режиме "Single-ended". Входной сигнал должен иметь постоянную составляющую +2,0 В и подаваться на позитивный вход ячейки ввода/вывода (рис. 2а). Недостатком такого подключения является то, что режим одиночного входа предполагает конфигурирование входной ячейки в режим фильтра низкой частоты с частотой среза от 76 до 470 кГц или программируемого усилителя с коэффициентом передачи от 16 до 128, что может наложить ограничения на характеристики входного сигнала.

Альтернативой может служить схема, приведенная на рис. 26. Как и в схеме на рис. 2а, сигнал на ПАИС поступает через позитивный дифференциальный вход, при этом на негативный вход подается постоянное напряжение +2,0 В, которое может быть получено от внутреннего источника опорного напряжения (вывод  $V_{\rm RMC}$ ). Необходимо отметить, что на выводе  $V_{\rm RMC}$  будет отсутствовать напряжение +2,0 В, а сам вывод будет находиться в третьем состоянии (высокоимпедансное или Z-состояние) до полной загрузки основной конфигурации в ПАИС.

Общим недостатком схем, представленных на рис. 2, является необходимость наличия постоянной составляющей входного сигнала.

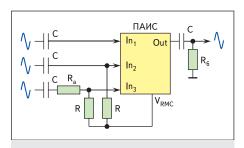

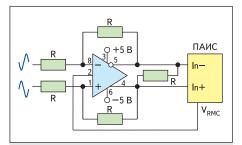

Необходимое смещение на вход ПАИС можно подавать от внутреннего источника опорного напряжения, предотвратив попадание постоянной составляющей на вход источника сигнала конденсатором (рис. 3, вход  $In_2$ ). В случае большой амплитуды входного сиг-

Рис. 2. Конфигурация ПАИС для работы с униполярным сигналом

**Рис. 3.** Подключение ПАИС к источнику биполярного сигнала через конденсаторы

нала последовательно с конденсатором можно установить резистор  $R_a$  (рис. 3, вход  $In_3$ ), который совместно с резистором R образует делитель.

Как правило, резистор R не требуется, исключение составляет случаи, когда первый конфигурируемый модуль (КАМ) является фильтром высокой частоты (билинейный или биквадратичный), дифференциатором (Differentiator), компаратором (Comparator), модулем выборки хранения (Hold) или выпрямителем с модулем выборки хранения (Rectifier Hold). Независимо от типа первого КАМа подтягивающий резистор R требуется (рис. 3, вход  $\rm In_2$ ), если входная ячейка сконфигурирована в режиме фильтра нижних частот (low-pass filter), усилителя с прерыванием (low offset chopper) или обычного усилителя (amplifier).

Недостаток схемы на рис. 3 в том, что сопротивление конденсаторов на самой низкой частоте должно быть минимальным, чтобы не произошло «завала» частотной характеристики на низкой частоте, поэтому номиналы резисторов и конденсаторов должны выбираться с максимально возможными значениями.

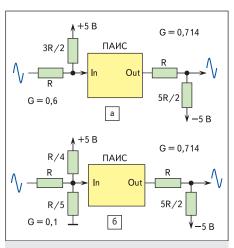

На рис. 4а и представлена схема сопряжения ПАИС Anadigm с источником биполярного сигнала, с помощью делителя с коэффициентом передачи G=0,6 постоянная составляющая входного сигнала обеспечивается равной +2,0 В. Входной делитель, представленный на рис. 46, имеет еще меньший коэффициент передачи G=0,1. Выходной делитель на обеих схемах с коэффициентом пе

**Рис. 4.** Схемы смещения нуля входного и выходного сигнала с помощью делителей на резисторах

редачи G=0,714 преобразует униполярный сигнал с постоянной составляющей  $+2,0\,$  В в биполярный сигнал.

Недостатком схем, представленных на рис. 4, является ослабление входного сигнала и использование высокоточных резисторов. Использование делителя на выходе может быть непригодно, если следующие за ПАИС каскады схемы имеют маленький входной импеланс.

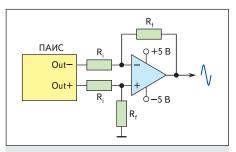

Для смещения уровня нуля слабых сигналов могут применяться операционные усилители (ОУ). На рис. 5 представлен входной каскад на операционном усилителе для смещения уровня нуля с 0 до +2 В. Использование

**Рис. 5.** Входной каскад, преобразующий биполярный сигнал в униполярный с постоянной составляющей, равной  $V_{RMC} = +2.0~B$

Рис. 6. Схема с использованием дифференциального усилителя AD8132 для преобразования биполярного дифференциального сигнала в однополярный дифференциальный

ОУ позволяет задать коэффициент усиления путем изменения отношений резисторов  $R_f$  и  $R_i$  в цепи обратной связи. Коэффициент усиления можно рассчитать по формуле  $K_y = R_f/R_i$ . Для предотвращения перегрузки по выходу  $V_{RMC}$  необходимо выбирать сумму резисторов  $R_f$  и  $R_i$  более 100 кОм. Для работы в режиме дифференциального входа понадобится такой же усилитель на второй

вход ПАИС, или нужно использовать диф-

ференциальный усилитель (рис. 6). Дифференциальный усилитель AD8132, используемый в схеме на рис. 6, имеет широкую полосу пропускания (350 МГц), поэтому для предотвращения эффекта наложения спектров рекомендуется включить конденсатор параллельно резисторам обратной связи. Так, при значениях номиналов резисторов R=500 Ом и конденсаторов в петле обратной связи C=1 нФ частота среза составит f=300 кГц.

#### Построение выходных цепей ПАИС

Самый простой способ удаления постоянной составляющей +2,0 В в выходном сигнале — использование на выходе ПАИС делителя на резисторах (рис. 4). Основной недостаток таких схем — влияние входного сопротивления последующих за ПАИС каскадов. Этот недостаток можно устранить, используя операционные усилители.

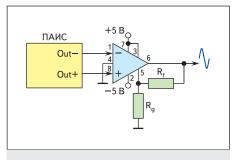

На рис. 7 представлен выходной каскад на OV для преобразования выходного униполярного дифференциального сигнала ПАИС в биполярный недифференциальный сигнал. Эта схема может использоваться для смещения уровня на любое другое напряжение, для этого достаточно подключить резистор  $\mathbf{R}_{\mathbf{f}}$  к требуемому напряжению. Преимущества использования такой схемы заключается в сохранении информации о постоянной составляющей дифференциального сигнала на выходе операционного усиления и низком выходном сопротивлении. Недостатком следует считать необходимость использования прецизионных резисторов.

На рис. 8 представлена схема формирования биполярного недифференциального сигнала из униполярного дифференциального

Рис. 7. Схема преобразования выходного униполярного дифференциального сигнала в биполярный недифференциальный сигнал

Рис. 8. Схема преобразования выходного униполярного дифференциального сигнала в биполярный сигнал с использованием ДУ AD8130

сигнала. Коэффициент усиления задается резисторами  $R_f$  и  $R_g$  и рассчитывается по формуле  $K_y=1+(R_f/R_g)$ . При соединении выводов 5 и 6 коэффициент усиления будет равен единице, при этом использование резисторов не требуется. Используя как основу схему на рис. 8, можно сформировать биполярный сигнал с любым значением «нуля», для этого на вывод 4 необходимо подать требуемое напряжение.

#### Заключение

Достаточная простота схемотехнической реализации входных каскадов для согласования уровней входного сигнала до значений, необходимых для работы ПАИС, позволяет быстро и эффективно реализовать программируемые аналоговые схемы на базе микросхем Anadigm.

#### Литература

- 1. AN121E04/AN221E04 Field Programmable Analog Arrays User Manual. www.anadigm.com

- Щерба А. Программируемые аналоговые ИС Anadigm: применение конфигурируемых аналоговых модулей в составе программы Anadigm-Designer2 // Компоненты и технологии. 2007. № 12.

- Щерба А. Программируемые аналоговые ИС Anadigm: подключение и загрузка конфигурационных данных с внешней микросхемы памяти при статическом конфигурировании (часть 1) // Современная электроника. 2008. № 8.