## Возможности двухканальных

## 14-битных радиочастотных ЦАП DAC38RFxx

В статье рассказывается о высокочастотных ЦАП семейства DAC38RFxx компании Texas Instruments, пригодных для использования в передатчиках базовых станций сотовой связи. В состав микросхем входят двухканальные повышающие преобразователи частоты, что позволяет подавать на их вход сигнал промежуточной частоты в стандартном формате IQ. Перестраиваемые цифровые фильтры, блоки автоматической регулировки усиления, усилители мощности и симметрирующие широкополосные выходные трансформаторы обеспечивают высокое качество радиочастотного сигнала.

Андрей САМОДЕЛОВ

#### Введение

Микросхемы DAC38RFxx — это семейство высокопроизводительных двухканальных 14-битных радиочастотных цифро-аналого-

вых преобразователей (ЦАП), с частотой дискретизации 9 ГГц (DAC38RF86, DAC38RF96) или 6,2 ГГц (DAC38RF87, DAC38RF97), способных синтезировать широкополосные сигналы в полосе частот 0–4,5 ГГц (DAC38RF86/96) или

0—3 ГТц (DAC38RF87/97). Спектральные характеристики выходного сигнала для микросхем семейства DAC38RFxx приведены в таблице 1.

Большой динамический диапазон позволяет использовать микросхемы семейства

www.kit-e.ru

GP00

**TESTMODE**

GP10

GP01

Рис. 2. Блок-схема DAC38RF96, DAC38RF97

DAC38RFxx (табл. 2) в широком классе приложений, таких как системы беспроводной связи GSM/3G(WCDMA)/4G(OFDM) и оборудование для их тестирования, широкополосные функциональные генераторы, SDR-радиостанции, радиолокаторы и системы спутниковой связи (SATCOM).

GND

SCLK

SLEEP

**Таблица 1.** Спектральные характеристики выходного сигнала ЦАП DAC38RFxx

| Параметры                   | DAC38RF87/97 | DAC38RF86/96 |                  |  |

|-----------------------------|--------------|--------------|------------------|--|

| f <sub>DAC</sub>            | 5898,24 МГц  | 8847,36 МГц  | 9 ГГц            |  |

| f <sub>out</sub>            | 2,14 ГГц     | 3,7 ГГц      | 1,8 ГГц, —6 dBFS |  |

| 20 MΓ <sub>Ц</sub> LTE ACLR |              | 66 дБн       |                  |  |

| IMD3                        |              |              | 70 дБн*          |  |

| WCDMA ACLR                  | 73 дБн       |              |                  |  |

| WCDMA alt-ACLR              | 77 дБн       |              |                  |  |

**Примечание.** \*Расстояние между тоновыми сигналами 10 МГц.

**Таблица 2.** Сравнение ЦАП DAC38RFxx

| Микро-<br>схема | Количество<br>каналов | Выход                                 | Интер-<br>поляция | Центральная<br>частота ГУН<br>(VCO), ГГц |

|-----------------|-----------------------|---------------------------------------|-------------------|------------------------------------------|

| DAC38RF86       | 2                     | Несим-<br>метричный<br>(Single ended) | 6-24              | 8,85                                     |

| DAC38RF96       |                       |                                       | 12-24             | 8,85                                     |

| DAC38RF87       |                       |                                       | 6-24              | 5,9                                      |

| DAC38RF97       |                       |                                       | 12-24             | 5,9                                      |

Микросхемы снабжены экономичным интерфейсом JESD204B, имеющим до восьми двунаправленных дифференциальных линий обмена данными (lane) с максимальной скоростью передачи до 12,5 Гбит/с, что позволяет получить скорость преобразования до 1,25×10 $^{9}$  отсчетов/с (GSPS) на канал. Каждый из каналов DAC38RFxx содержит два повышающих цифровых преобразователя частоты с различными вариантами интерполяции. Для поддержки многодиапазонных операций служат цифровой квадратурный модулятор и независимые генераторы с цифровым управлением частотой (NCO). Для упрощения системы тактирования в ЦАП встроен GSMсовместимый ГУН с ФАПЧ (PLL/VCO) с низким уровнем фазового шума, чтобы использовать низкочастотные тактовые генераторы.

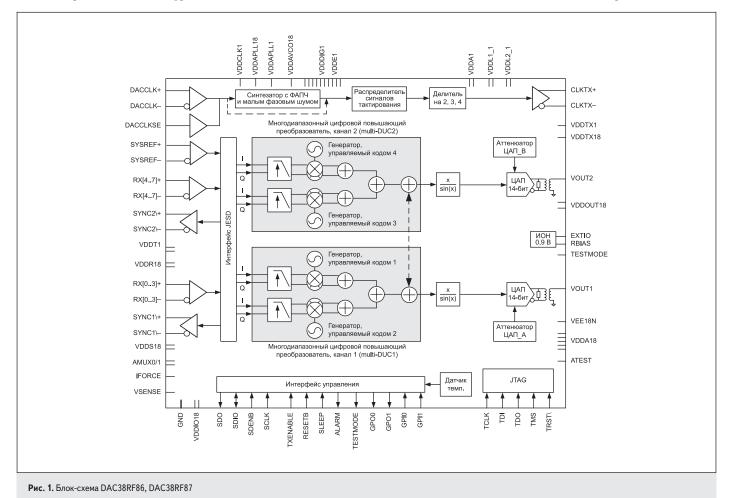

Блок-схема ЦАП DAC38RF86, DAC38RF87 приведена на рис. 1, а ЦАП DAC38RF96, DAC38RF97 — на рис. 2.

#### Функциональные особенности

Далее рассмотрены функциональные особенности микросхем семейства DAC38RFxx.

#### Входы SerDes

<u>F</u> 6

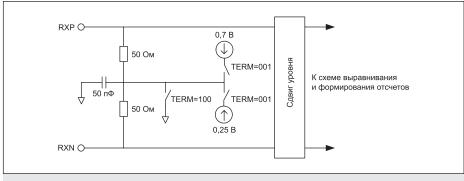

Каждый из дифференциальных входов RX[0..7]+/– микросхем DAC38RFxx имеет внутренний подтягивающий к общей шине резистор сопротивлением 50 Ом (рис. 3).

Рис. 3. Согласование дифференциальных входов с линией

В общем случае согласование осуществляется подключением конденсатора емкостью 50 пФ между входом и общей шиной (GND). Тип согласования для дифференциального сигнала можно выбирать в зависимости от требований приложения посредством поля TERM регистра SRDS\_CFG2.

Выборка входных данных производится дифференциальным усилителем, использующим восстановленный с помощью специального алгоритма сигнал тактирования. Полярность RX+ и RX- для дифференциальной пары можно инвертировать установкой в «1» соответствующего бита INVPAIR регистра SRDS\_POL. Это потенциально может упростить топологию печатной платы и улучшить целостность сигнала, предотвращая необходимость перекрещивания дорожек на печатной плате.

Из-за неидеальности дифференциального усилителя по каналам RX+ и RX- в пороге переключения присутствует смещение. ЦАП DAC38RFxx содержит схему обнаружения и коррекции этого смещения. Функция включается установкой бита ENOC регистра SRDS\_CFG1 в «1». Предполагается, что большинство пользователей будут применять эту функцию. В процессе компенсации поле LOOPBACK регистра SRDS\_CFG1 необходимо устанавливать в «00».

#### Пропускная способность SerDes

ЦАП DAC38RFxx имеет восемь конфигурируемых линий JESD204B, с максимальной скоростью обмена для каждой SerDes пары 12,5 Гбит/с. Поскольку первичная рабочая частота SerDes определяется частотой тактирования и множителем ФАПЧ (PLL), имеется ограничение на нижнюю частоту, поддерживаемую SerDes. Для обеспечения низкоскоростных приложений каждый приемник должен конфигурироваться для работы на 1/2, 1/4 или 1/8 от полной частоты тактирования посредством поля RATE регистра SRDS\_CFG2.

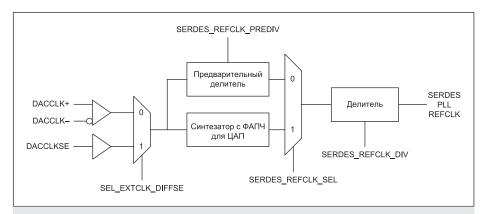

### Синтезатор частоты с ФАПЧ (PLL) для SerDes

ЦАП DAC38RFxx имеет два встроенных синтезатора с ФАПЧ (PLL): один обеспечивает тактирование ЦАП; второй — интерфейca SerDes. Опорная частота для SerDes PLL может находиться в диапазоне 100-800 МГц (оптимальное значение 300-800 МГц). Опорная частота от DACCLK делится на значение, записанное в поле SerDes REFCLK DIV регистра SRDS\_CLK\_CFG, как показано на рис. 4. Поле SerDes\_CLK\_SEL регистра SRDS\_CLK\_CFG задает, будет ли в качестве источника опорной частоты для SerDes PLL применен вход DACCLK или выход DAC PLL. Если необходим вход DACCLK, то для уменьшения частоты DACCLK должен использоваться предварительный делитель, заданный полем SerDes\_REFCLK\_PREDIV регистра SRDS\_CLK\_CFG.

Рис. 4. Опорная частота для SerDes PLL

При нормальной работе частота генерации синтезатора с ФАПЧ (PLL) в 4–25 раз выше частоты опорного сигнала тактирования, в соответствии с множителем, задаваемым полем MPY регистра SRDS\_PLL\_CFG. Перед выбором значений множителя и опорной частоты необходимо определить выходную частоту для ФАПЧ. Соотношение между выходной частотой ФАПЧ (PLL) и скоростью обмена по дифференциальным парам задается полем RATE регистра SRDS\_CFG2. Имея вычисленную выходную частоту ФАПЧ (PLL), необходимое значение опорной частоты можно определить делением значения этой частоты на множитель MPY.

Широкий диапазон значений множителя совместно с различными режимами работы позволяет достичь заданной скорости обмена по дифференциальным парам (line rate) при множестве различных значений опорной частоты. Предпочтительной является комбинация с максимальным значением опорной частоты.

Значение частоты ГУН (VCO) системы ФАПЧ (PLL) SerDes должно находиться в диапазоне частот 1,5625—3,125 ГГц. В зависимости от рабочей частоты ГУН (VCO) необходима подстройка полосы фильтра обратной связи (loop filter). Если выходная частота ФАПЧ (PLL) ниже 2,17 ГГц, то бит VRANGE регистра SRDS\_PLL\_CFG должен быть установлен в «1».

Производительность встроенной системы  $\Phi$ АПЧ (PLL) можно оптимизировать в соответствии со значением фазового шума (jitter) опорного тактового сигнала выбором соответствующей полосы пропускания петли обратной связи (loop bandwidth) системы  $\Phi$ АПЧ (PLL) и значения для поля LB регистра SRDS\_PLL\_CFG. Ширину полосы пропускания петли обратной связи можно получить, разделив значение опорной частоты тактирования на коэффициент BWSCALE, который зависит от значения LB и выходной частоты  $\Phi$ АПЧ (PLL).

Для большинства систем, где опорная частота тактирования заводится в микросхему через входной буфер с низким фазовым шумом (jitter), подходит и рекомендована шири-

на полосы пропускания петли обратной связи системы ФАПЧ, примерно равная 8-30 МГц. Для систем, в которых опорная частота тактирования заводится через входной буфер с низким фазовым шумом (jitter), но имеет низкое качество, с целью лучшей фильтрации полосу пропускания выбирают меньше 8 МГц. Для систем, в которых опорная частота тактирования очищается основанной на LCконтуре системой с ФАПЧ с ультранизким значением фазового шума (jitter), в большинстве случаев ширина полосы пропускания петли обратной связи может достигать 60 МГц. Следует отметить, что ультравысокая ширина полосы пропускания не рекомендуется для коэффициента умножения системы ФАПЧ (PLL) меньшего, чем 8.

Свободный выход тактового генератора доступен, если бит ENDIVCLK регистра SRDS\_PLL\_CFG установлен в «1». При работе с фиксированным коэффициентом деления выходной частоты ФАПЧ, равным 80, может быть выведен сигнал ALARM установкой поля DTEST регистра DTEST в «0001» (для дифференциальных пар 0–3) или «0010» (для дифференциальных пар 4–7).

## Система адаптивной коррекции интерфейса SerDes

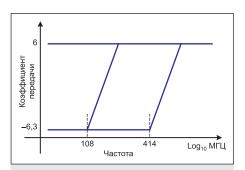

Все каналы DAC38RFxx содержат системы адаптивной коррекции (equalizer), которые могут компенсировать вносимые каналом потери ослаблением низкочастотных компонентов в соответствии с амплитудой высокочастотных компонентов, таким образом уменьшая интерференцию между отсчетами. На рис. 5 показан частотный отклик корректирующей цепи (equalizer) — его можно описать в терминах значения коэффициента усиления на низких частотах и частоты, до которой коэффициент усиления остается неизменным (то есть частоты нуля). Выше нулевой частоты коэффициент передачи растет со скоростью 6 дБ/октава до тех пор, пока не достигнет значения коэффициента передачи на высоких частотах.

Систему адаптивной коррекции можно сконфигурировать посредством полей EQ и EQHLD in peructpa SRDS\_CFG1. После

Рис. 5. Частотный отклик корректирующей цепи

активации корректирующая логика приемника анализирует паттерны и время прохождения данных, чтобы определить, требуется ли увеличить или уменьшить низкочастотный коэффициент передачи. Логика принятия решения реализована в виде алгоритма голосования с относительно большим интервалом анализа. Большая постоянная времени уменьшает возможность неправильного принятия решения и позволяет корректирующей цепочке компенсировать относительно стабильный ответ канала. Время блокировки для системы адаптивной коррекции зависит от данных, поэтому для него невозможно задать применимое во всех случаях значение. Однако в предположении случайности данных максимальное время блокировки составит  $6 \times 10^6$ , деленное на уровень активности CDR.

#### Дешифратор JESD204B (descrambler)

Доступен 16-битный параллельный самосинхронизируемый дешифратор (descrambler), основанный на полиноме  $1+x^{14}+x^{15}$ . В соответствии со спецификацией JESD204В процедура зашифрования/расшифрования (scrambling/descrambling) применяется только к пользовательским данным и не используется при синхронизации групп кода или последовательности ILA. Каждый многоканальный цифровой повышающий преобразователь (multi-DUC) имеет отдельный дешифратор (descrambler), активируемый независимо от других дешифраторов. Дешифратор (descrambler) активируется установкой поля SCR в страничном регистре JESD\_N\_HD\_SCR преобразователя (multi-DUC).

#### Сборка кадра JESD204B

Микросхема DAC38RFxx может быть запрограммирована для работы в режиме одиночного (single DAC) или сдвоенного (dual DAC) ЦАП, с отдельным блоком JESD RX, спроектированным для каждого ЦАП. Два блока JESD RX программируются для работы в качестве двух отдельных каналов обмена данными (link) или в качестве единого канала.

#### Интерфейс SYNK

Интерфейс JESD204B микросхем DAC38RFxx имеет два дифференциальных выхода <u>SYNK</u>, которые называются <u>SYNK0</u>

и SYNK1. Они предназначены для поддержки двух каналов обмена данными. Кроме того, в качестве несимметричных (singleended) выходов сигналов SYNK с уровнями КМОП (CMOS) могут быть использованы линии ввода/вывода общего назначения GPO0 и GPO1.

Каждый из дифференциальных или КМОП (CMOS) выходов включается посредством 2-разрядного регистра (поля GPO0\_ SEL, GPO1\_SEL, SYNC0B\_SEL, SYNC1B\_SEL регистра IO\_CONFIG). При этом бит 0 управляет сигналом SYNK для multi-DUC1, а бит 1 управляет сигналом SYNK для multi-DUC2 SYNC. Если оба DUC-преобразователя активны, то сигналы <u>SYNK</u> объединяются по ИЛИ (OR).

Сигнал <u>SYNK</u> может удерживаться приемником на низком (low) уровне или для запроса на синхронизацию, чтобы инициализировать/переинициализировать линию обмена данными или сообщить передатчику об ошибке обмена данными. Запрос на синхронизацию должен иметь длительность как минимум в пять кадров плюс девять октетов, с округлением до размера ближайшего количества кадров. Для сообщения об ошибке сигнал <u>SYNK</u> должен удерживаться в течение длительности двух кадров. Передатчик интерпретирует любой спадающий фронт на своем входе <u>SYNK</u> как ошибку и любое удержание сигнала <u>SYNK</u> в течение четырех кадров или более как запрос на синхронизацию.

#### Конфигурация с одноили двухканальным обменом данными

Интерфейс JESD204B микросхем DAC38RFxx можно сконфигурировать для работы в одно- или двухканальном режиме. Преимуществом двухканального режима, по одному каналу на каждый ЦАП, является то, что один из каналов можно переинициализировать без влияния на второй канал. При этом возможны три варианта конфигурации (табл. 3).

#### Синхронизация систем из нескольких микросхем ЦАП

Во многих приложениях, таких как системы с множеством приемных антенн, в которых вычисляются корреляции между

информацией из различных каналов, требуется, чтобы задержки в каналах были детерминированы и различные ЦАП были с высокой точностью синхронизированы таким образом, чтобы их выходной сигнал оказался выровненным по фазе. Для микросхем DAC38RFxx детерминированность задержки определяется использованием сигнала SYSREF (JESD204B Subclass 1).

Сигнал SYSREF генерируется тем же самым блоком тактирования, что и DACCLK. После ресинхронизации собственного тактового генератора (local multi-frame clock, LMFC) относительно SYSREF, ЦАП потребует ресинхронизацию канала обмена данными через интерфейс SYNC. Обработку сигнала на входе SYSREF можно разрешить или запретить через SPI-интерфейс.

#### Схема захвата сигнала SYSREF

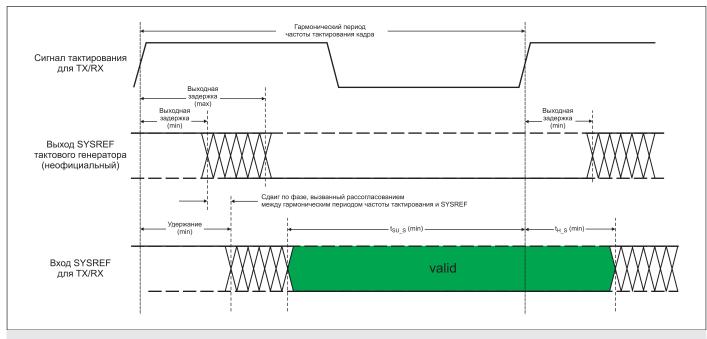

Стандарт JESD204B для устройств Device Subclass 1 вводит сигнал SYSREF, который можно использовать в качестве глобальной метки времени для выравнивания по фазе внутренних систем тактирования (local multiframe clock, LMFC) и тактирования кадров данных в системах, состоящих из нескольких ЦАП. Это обеспечивает в системе детерминированную задержку и выравнивает отсчеты данных для нескольких ЦАП одновременно. Сигнал SYSREF достигает этой цели, идентифицируя фронты сигнала тактирования для каждой микросхемы, которую затем можно использовать в качестве образцовой при синхронизации следующих микросхем. В частности, LMFC и сигнал тактирования кадров выравниваются по сигналу тактирования микросхемы, когда сигнал SYSREF переходит из «0» в «1». Сигнал SYSREF (рис. 6) может быть периодическим, однократным или кусочно-периодическим ("gapped" periodic), и его период должен быть кратным периоду сигнала тактирования, вырабатываемого LMFC.

При тактировании высокоскоростных устройств фазы сигналов SYSREF относительно сигнала тактирования устройства должны удовлетворять требованиям на время установки/фиксации (setup/hold time) для каждого индивидуального тактового генератора. Исторически это достигается контролем задержек в проводниках печатной пла-

Таблица 3. Конфигурация режимов обмена данными

| Nº | Режим                                                   | Настройка                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | Двойной ЦАП,<br>двухканальный режим<br>обмена данными   | а) Запрограммировать поля с OCTETPATHO_SEL по OCTETPATH7_SEL в страничном регистре JESD_CROSSBART и JESD_CROSSBARZ модулей multi-DUC таким образом, чтобы каждый multi-DUC принимал данные из соответствующего канала SerDes.  6) Установить соответствующие биты поля LANE_ENA страничного регистра JESD_LN_EN модулей multi-DUC таким образом, чтобы обеспечить использование модулями multi-DUC каналов обмена данными.  в) Установить бит ONE_DAC_ONLY регистра RESET_CONFIG в «0» (по умолчанию).                          |

| 2  | Двойной ЦАП,<br>одноканальный режим<br>обмена данными   | а) Запрограммировать поля с ОСТЕТРАТНО SEL по ОСТЕТРАТН7 SEL в страничном регистре JESD_CROSSBART и JESD_CROSSBARZ модулей multi-DUC таким образом, чтобы каждый multi-DUC принимал данные из соответствующего канала SerDes.  6) Установить соответствующие биты поля LANE_ENA страничного регистра JESD_LN_EN модулей multi-DUC таким образом, чтобы обеспечить использование модулями multi-DUC-каналов обмена данными.  8) Установить бит ONE_LINK_ONLY регистра RESET_CONFIG в «1», чтобы сконфигурировать выход ТХЕNABLE. |

| 3  | Одиночный ЦАП,<br>одноканальный режим<br>обмена данными | а) Установить бит ONE_DAC_ONLY регистра RESET_CONFIG в «1», чтобы отключить тактирование multi-DUC2 для уменьшения энергопотребления. б) Значение бита ONE_LINK_ONLY в данном случае не играет роли.                                                                                                                                                                                                                                                                                                                            |

Рис. 6. Синхросигнал SYSREF

ты и/или с помощью коммерческих систем распределенного тактирования, способных генерировать сигналы тактирования микросхем и сигналы SYSREF с программируемой задержкой и возможностью разделения исходного сигнала SYSREF на множество сигналов SYSREF, каждый из которых имеет собственную задержку с тонкой подстройкой ее величины. Поскольку семейство DAC38RFxx поддерживает сигналы тактирования с частотой до 9 ГГц, схема захвата SYSREF включена в состав DAC38RFxx, что позволяет расслабиться в отношении установки и фиксации тактового сигнала.

Схема захвата сигнала SYSREF обеспечивает:

- чувствительность к изменениям фазы сигнала SYSREF, обусловленным особенностями изготовления микросхем и их окружения в реальном устройстве;

- нечувствительность к ошибкам захвата, обусловленным установкой/фиксацией/метастабильностью;

- информацию о соотношении между фазами сигнала SYSREF и сигнала тактирования ЦАП внутри микросхемы;

- программную компенсацию рассогласования сигналов по фазе, вызванных ошибками в топологии печатной платы.

#### Поддержка JESD204B Subclass 0

В микросхемах реализована функциональность для поддержки работы в режиме Subclass 0. Следует отметить, что программирование параметров конфигурации SUBCLASSV не оказывает функционального влияния на остальную логику. Запрограммированные для SUBCLASSV значения используются только при начальном выравнивании сигнала в дифференциальных парах (initial lane alignment, ILA).

# Многодиапазонный повышающий преобразователь частоты (multi-DUC)

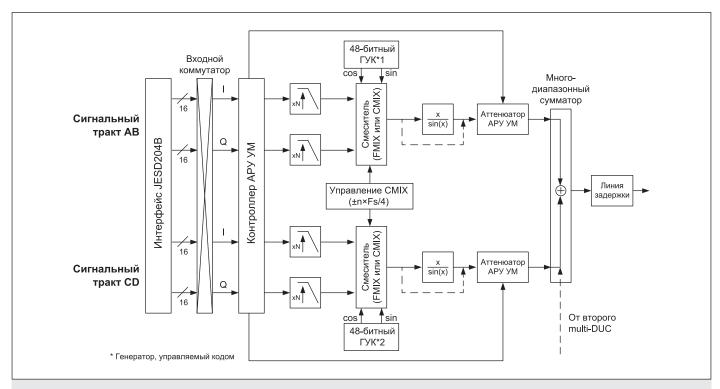

Выход каждого канала ЦАП в DAC38RFxx снабжен двухдиапазонным повышающим преобразователем частоты (dual band digital up-converter, DUC), называемым multi-DUC. На рис. 7 показаны функции обработки сигналов каждого из двух multi-DUC. Оба тракта обработки сигнала идентичны и независимы. Регистры с SPI-интерфейсом для multi-DUC имеют страничную адресацию, при этом страница 0 (page 0) поддерживает multi-DUC1, а страница 1 (раде 1) поддерживает multi-DUC2. Регистр PAGE\_SET предусмотрен для выбора страницы. Одновременно могут быть выбраны обе страницы, что позволяет параллельно программировать оба multi-DUC одними и теми же параметрами.

Каждый multi-DUC имеет два канала преобразования (DUC), называемых «тракт AB» и «тракт CD». Выходной сигнал одного multi-DUC можно сложить с выходным сигналом другого multi-DUC, чтобы получить конфигурацию с четырьмя просуммированными выходами DUC для одного ЦАП. После

**Таблица 4.** КИХ-фильтры, используемые для различной частоты интерполяции

| Порядок<br>интерполяции | FIR0 (2x) | FIR1 (2x) | LPFIR0_5X | FIR2 (2x) | LPFIR0_3X | FIR3 (2x) | LPFIR1_3X |

|-------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| 6                       | х         |           |           |           | х         |           |           |

| 8                       | х         | х         |           | х         |           |           |           |

| 10                      | х         |           | х         |           |           |           |           |

| 12                      | х         | х         |           |           |           |           | х         |

| 16                      | х         | х         |           | х         |           | х         |           |

| 18                      | х         |           |           |           | х         |           | х         |

| 20                      | х         | х         | х         |           |           |           |           |

| 24                      | х         | х         |           | х         |           |           | х         |

квадратурного модулятора установлен компенсирующий фильтр  $\sin(x)/x$ , за которым следует многодиапазонный блок суммирования (multiband summation block), имеющий возможность добавлять сигналы от других multi-DUC для получения комбинированного четырехканального DUC, каждый с независимым управлением частотой. Конечным в цепочке является блок задержки выходного сигнала (output delay block) с диапазоном задержки 0—15 отсчетов.

#### Вход multi-DUC

Каждый multi-DUC может принимать данные с восьми каналов (lane) интерфейса SerDes. Коммутатор (crossbar switch) позволяет менять местами любую пару каналов (lane) интерфейса SerDes. Коммутатор (crossbar switch) управляется полями OCTETPATHx\_SEL (x = [0-7]) регистров JESD\_CROSSBAR1 и JESD\_CROSSBAR2.

Многодиапазонный DUC-конвертер можно сконфигурировать или как одиночный DUC с одним входом IQ input, или как сдвоенный DUC с двумя входами IQ установкой поля DUAL\_IQ регистра MULTIDUC\_CFG1.

#### Интерполяционные фильтры

Цифровой повышающий преобразователь частоты (up-converter) вначале увеличивает частоту отсчетов IQ-сигнала от входной частоты отсчетов до конечной частоты отсчетов ДАП, используя ряд интерполяционных фильтров. Для получения различной конечной частоты отсчетов предлагается набор различных фильтров, как показано в таблице 4. Порядок интерполяции выбирают посредством поля INTERP регистра MULTIDUC CFG1.

КИХ-фильтры спроектированы с полосой пропускания ВW, равной 0,4× $f_{

m INPUT}$ , внепо-

Рис. 7. Блок-схема обработки сигнала в блоке multi-DUC микросхем DAC38RFxx

лосным затуханием 90 дБн и неравномерностью частотной характеристики <0,001 дБ. Комбинированная частотная характеристика для каждого коэффициента интерполяции показана на рис. 42-49 документа [1].

#### Цифровой квадратурный модулятор

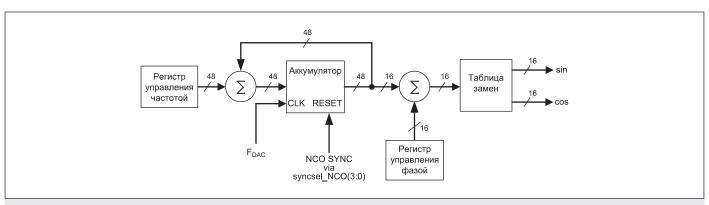

Каждый DUC-преобразователь в микросхемах DAC38RFxx имеет блоки цифрового квадратурного модулятора (digital quadrature modulator, DQM) с независимыми генераторами, управляемыми цифровым кодом (Numerically Controlled Oscillator, NCO), которые преобразуют сложный входной сигнал в реальный сигнал с гибким расположением несущей в диапазоне  $0-f_{\rm DAC}/2$ . Генераторы NCO активируются полями NCOAB\_ENA и NCOCD\_ENA регистра MULTIDUC\_CFG2. Каждый из NCO имеет 48-разрядные регистры установки частоты (FREQ\_NCOAB и FREQ\_NCOCD) и 16-разрядные регистры установки фазы (PHASE\_NCOAB и PHASE\_NCOCD), которые генерируют синусный и косинусный сигналы для сложного смешивания. Блок-схема NCO показана на рис. 8.

Синхронизация генераторов NCO осуществляется сбросом аккумуляторов NCO в ноль. Источник синхронизации выбирают с помощью полей SYNCSEL\_NCOAB и SYNCSEL\_NCOCD регистра

SYNCSEL1. Слово управления частотой из регистров FREQ\_NCOAB и FREQ\_NCOCD добавляется к значению аккумуляторов каждый период частоты тактирования  $f_{\rm DAC}$ .

Частота и сдвиг фазы для генераторов NCO вычисляется по формулам:

$$f_{\text{NCO AB (или CD)}} = F_{\text{REQ NCO AB (или CD)}} \times f_{\text{DAC}} / 2^{48},$$

(1)

$$\delta_{AB\,(\text{или CD})} = 2\pi \times (PHASE\_NCO\,AB\,(\text{или CD})/2^{16}).$$

(2)

Рассматривая сигналы в каналах как комплексные векторы в форме I+jQ, для сигнала на выходе DQM получим соотношение:

$$\begin{aligned} &Output_{AB} = \{I_{\text{INPUTAB}} \times \cos(2\pi \times f_{\text{NCOAB}} \times t + \delta_{\text{AB}}) - \\ &-Q_{\text{INPUTAB}} \times \sin(2\pi \times f_{\text{NCOAB}} \times t + \delta_{\text{AB}})\} \times 2^{\text{MIXERAB\_GAIN-1}}, \end{aligned} \tag{3}$$

$$\begin{aligned} Output_{CD} &= \{I_{\text{INPUTCD}} \times \cos{(2\pi \times f_{\text{NCOCD}} \times t + \delta_{\text{CD}})} - \\ &- Q_{\text{INPUTCD}} \times \sin{(2\pi \times f_{\text{NCOCD}} \times t + \delta_{\text{CD}})} \} \times 2^{\text{MIXERCD\_GAIN-1}}, \end{aligned} \tag{4}$$

где t — это время с момента последнего сброса аккумулятора NCO и значения полей MIXERAB\_GAIN и MIXERCD\_GAIN регистра MULTIDUC\_CFG2, которые могут быть равны 0 или 1.

Рис. 8. Блок-схема NCO

Рис. 9. Спектр амплитуды INVSINC

Максимальная выходная амплитуда DQM достигается, если  ${\rm I_{IN}}(t)$  и  ${\rm Q_{IN}}(t)$  имеют одновременно полный размах амплитуды и аргументы функций  ${\rm sin}()$  и  ${\rm cos}()$  равны целым кратным  $\pi/4$ .

При MIXERAB\_GAIN или MIXERCD\_GAIN = 0 коэффициент передачи DQM равен sqrt(2)/2, или -3 дБ. Потери мощности сигнала в большинстве случаев являются нежелательными, поэтому рекомендуется, чтобы для компенсации использовалась функция усиления на 3 дБ. При MIXERAB\_GAIN или MIXERCD\_GAIN = 1 коэффициент передачи DQM равен sqrt(2) или +3 дБ, что может привести к ограничению сигнала, если  $I_{\rm IN}(t)$  и  $Q_{\rm IN}(t)$  одновременно имеют полный размах амплитуды и поэтому должны использоваться с осторожностью.

## Смешанные режимы с грубым разрешением и низким энергопотреблением

Дополнительно генератор NCO микросхем DAC38RFxx имеет блок грубого смесителя (coarse mixer), способный сдвигать спектр входного сигнала на фиксированную частоту  $\pm N \times f_{\rm DAC}/8$ . Использование блока грубого смесителя (coarse mixer) вместо полнофункциональных смесителей (full mixer) приведет к уменьшению энергопотребления.

Рассматривая два комплексных канала как комплексные векторы в форме I(t)+jQ(t), выходной сигнал грубого смесителя (coarse mixer) можно представить в виде:

$$Output_{AB} = I_{\text{INPUTAB}} \times \cos(2\pi \times f_{\text{CMIX\_AB}} \times t) - Q_{\text{INPUTAB}} \times \sin(2\pi \times f_{\text{CMIX\_AB}} \times t), \tag{5}$$

$$\begin{aligned} Output_{CD} &= I_{\text{INPUTCD}} \times \cos(2\pi \times f_{\text{CMIX\_CD}} \times t) - \\ &- Q_{\text{INPUTCD}} \times \sin(2\pi \times f_{\text{CMIX\_CD}} \times t), \end{aligned} \tag{6}$$

где  $f_{\rm CMIX\_AB}$  и  $f_{\rm CMIX\_CD}$  — это фиксированные частоты смешения, выбираемые полями CMIX\_AB или CMIX\_CD регистра CMIX. Блоки грубых смесителей (coarse mixer) отключаются установкой CMIX\_AB и CMIX\_CD в 0x0.

Генератор NCO и грубые смесители (coarse mixer) можно активировать независимо, хотя в большинстве случаев это неудобно, поскольку NCO может перекрываться полный рабочий диапазон.

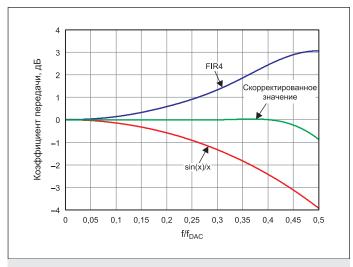

#### Инверсный Sinc-фильтр

Микросхемы DAC38RFxx имеют 9-каскадный инверсный Sinc-фильтр (INVSINC), который работает на частоте обновления данных ЦАП ( $f_{\rm DAC}$ ) и может использоваться для сглаживания частотной характеристики выхода УВХ (sample-and-hold). Выход УВХ ЦАП устанавливает выходной ток и удерживает его постоянным для одного периода тактирования ЦАП до тех пор, пока следующий отсчет не приведет к хорошо известному частотному отклику типа  $\sin(x)/x$

или  $\operatorname{sinc}(x)$  (красная линия на рис. 9). Ответ инверсного Sinc-фильтра (синяя линия на рис. 9) имеет противоположный частотный отклик в пределах 0–0,4× $f_{\mathrm{DAC}}$ , что приводит к смешанному ответу (зеленая линия на рис. 9). В интервале 0–0,4× $f_{\mathrm{DAC}}$  инверсный Sinc компенсирует спад частотной характеристики VBX с ошибкой менее 0,03 дБ.

Инверсный Sinc-фильтр имеет коэффициент передачи >1 для всех частот. Поэтому для предотвращения насыщения фильтра амплитуда входного сигнала INVSINC должна быть уменьшена относительно полного размаха. Необходимый коэффициент ослабления (back-off) зависит от частоты сигнала и выбирается таким образом, чтобы в рабочем диапазоне частот комбинация входного сигнала и ответа фильтра была меньше 1 (0 дБ). Например, если поступающий на вход INVSINC сигнал имеет частоту  $0.25 \times f_{\rm DAC}$ , то ответ от INVSINC равен 0,9 дБ, и для предотвращения перегрузки сигнал должен быть ослаблен на 0,9 дБ относительно полного размаха. Важное преимущество того, что INVSINC имеет положительный коэффициент передачи на всех частотах, заключается в том, что пользователь может оптимизировать ослабление сигнала, основываясь на его частоте.

Инверсные Sinc-фильтры активируются полем ISFIR\_ENA регистра MULTIDUC\_CFG1.

#### Блок суммирования для режимов Dual DUC

При использовании режимов dual DUC выходные сигналы с двух блоков AQM суммируются вместе для формирования смешанного сигнала для выхода ЦАП, конфигурируемого полем OUTSUM\_SEL регистра OUTSUM. Входные сигналы для DUC-преобразователей должны быть масштабированы таким образом, чтобы при суммировании амплитуда полученного сигнала не достигала полной шкалы. Это поле можно сконфигурировать и для смешивания сигналов от смежных multi-DUC для получения четырех сигналов от DUC.

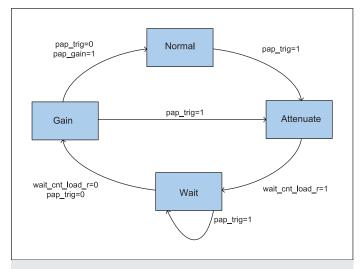

#### Блок защиты усилителя мощности (PA Protection Block, PAP)

В состав DAC38RFxx входит дополнительный блок защиты усилителя мощности (power amplifier protection, PAP) для отслеживания моментов, когда входной сигнал становится слишком большим, например при возникновении ошибок в интерфейсе передачи данных, и уменьшает мощность выходного сигнала ЦАП.

Блок РАР реализует функцию уменьшения входного сигнала, который превышает пороговое значение, с помощью трех основных подблоков: блока генерации сигнала запуска РАР, машины состояний для подстройки коэффициента передачи РАР и блока регулирования коэффициента передачи (GAIN).

Блок РАР отслеживает мощность входного сигнала путем накопления с помощью скользящего окна последних N отсчетов. Значение N выбирают равным 32, 64 или 128 на основании настроек поля PAPAB\_SEL\_DLY регистра PAP\_CFG\_AB и поля PAPCD\_SEL\_DLY регистра PAP\_CFG\_CD. Усредненная амплитуда входного сигнала вычисляется делением накопленного значения на количество отсчетов в линии задержки (N). Затем результат сравнивается с пороговыми значениями в поле PAPAB\_THRESH регистра PAP\_CFG\_AB и поле PAPCD\_THRESH регистра PAP\_CFG\_CD. Если пороговое значение окажется превышенным, запускается машина состояний, которая генерирует значение для уменьшения средней амплитуды выходного сигнала ЦАП. После того как входной сигнал возвращается к нормальному значению, машина состояний вновь увеличивает амплитуду выходного сигнала ЦАП.

Генерация сигнала, запускающего PAP, происходит следующим образом:

- отсчеты в каналах I и Q рассматриваются как независимые каждый из них может запустить процесс ослабления выходного сигнала;

- в режимах dual DUC каждая пара IQ рассматривается отдельно и имеет отдельный блок регулировки коэффициента передачи;

- 8 входных отсчетов проходят через схему вычисления абсолютного значения сигнала (все в формате дополнения до 2);

- далее эти значения суммируются в векторной форме для получения 12 бит результата;

- затем 12 бит результата помещаются в линию задержки и суммируются в аккумуляторе;

- из значения аккумулятора вычитается задержанное 12-битное слово, соответствующее N = 32, N = 64 или N = 128;

- в конце выходное значение аккумулятора делится на N и округляется до 13 бит, которые сравниваются с пороговым значением, хранящимся в SPI-регистрах. При превышении порога возникает событие pap\_trig.

Машина состояний коэффициента передачи РАР генерирует значение коэффициента передачи, применяемое к выходному потоку, чтобы уменьшить амплитуду выходного сигнала. Машина состояний используется для ослабления выходного сигнала ЦАП и его возрастания до исходного состояния после снятия сигнала, запускающего подстройку коэффициента усиления.

Нормальным рабочим условием блока РАР является нормальное состояние (NORMAL) на диаграмме, приведенной на рис. 10. Однако если блок РАР обнаруживает ошибочные условия, то он устанавливает сигнал pap\_trig в «1», что вызывает переход из нормального состояния (NORMAL) в состояние ослабления входного сигнала (ATTENUATE).

В состоянии ослабления ATTENUATE коэффициент передачи тракта прохождения сигнала может меняться от 1.0 до 0.0 с программируемым шагом, задаваемым значением поля PAPAB\_GAIN\_STEP регистра PAP\_GAIN\_AB и поля PAPCD\_GAIN\_STEP регистра PAP\_ GAIN\_CD. Это значение всегда положительное с десятичным разделителем, расположенным между MSB и MSB-1. Единичному коэффициенту передачи соответствует значение 1000000000. В течение каждого периода тактовой частоты (16 отсчетов) значение PAP\_GAIN уменьшается на PAPAB\_GAIN\_STEP и PAPCD\_GAIN\_STEP до тех пор, пока коэффициент передачи не уменьшится до 0.

После того как значение PAP\_GAIN станет равным 0, машина состояний переходит в состояние ожидания (WAIT). В данном состоянии программируемый счетчик подсчитывает периоды сигнала тактирования, чтобы позволить зафиксироваться значению для pap\_trig. Поле PAPAB\_WAIT регистра PAP\_WAIT\_AB и поле PAPCD\_WAIT регистра PAP\_WAIT\_CD используются для выбора количества периодов сигнала тактирования (количество отсчетов равно 16×PAPAB\_WAIT или 16×PAPCD\_WAIT) ожидания перед переходом в следующее состояние. После того как значение счетчика ожидания (WAIT counter) станет равным нулю и pap\_trig = 0, машина состояний переходит в состояние подстройки коэффициента передачи (GAIN). Если значение счетчика ожидания равно 0, а значение pap\_trig все еще равно 1, то машина состояний остается в состоянии ожидания (WAIT) до тех пор, пока не будет выполнено условие  $pap_trig = 0$ .

#### Блок подстройки коэффициента передачи (Gain Block)

Блок подстройки коэффициента передачи (GAIN block) обеспечивает дополнительное управление выходным сигналом с помощью поля GAINAB регистра GAINAB и поля GAINCD регистра GAINCD. Аналогично значению PAP\_GAIN, выходной коэффициент передачи всегда положительный и равен единице, когда значение GAINAB или GAINCD = 0100000000000.

Для уменьшения энергопотребления тактирование блока GAIN отключается, когда выключена вся подсистема PAP и GAINAB или GAINCD устанавливается в 1.

#### Выходное суммирование

Блок OUTSUM позволяет складывать отсчеты от каждого DUC в multi-DUC. Кроме того, он разрешает складывать выходные от смежных multi-DUC. Поле OUTSUM\_SEL регистра OUTSUM управляет режимом суммирования для каждого multi-DUC. Функционирование блока можно представить следующим уравнением:

$$OUTSUM_{output} = SAME_{AB} + SAME_{CD} + ADJ_{AB} + ADJ_{CD}. \tag{7}$$

Для предотвращения переполнения после сложения выполняется операция округления, чтобы вернуть длину слова обратно к 16 бит.

Рис. 10. Машина состояний регулировки коэффициента передачи РАР

Количество округляемых битов зависит от количества добавленных каналов.

#### Выходная задержка

После выходного суммирования сигнал может быть программным путем задержан на 0-15 тактов DACCLK с помощью поля OUTPUT\_DELAY регистра OUTSUM. Блок принимает 16 слов отсчетов (vec16) из обоих трактов А и В и затем сдвигает их в линии задержки длиной 32 бит.

#### Инвертирование полярности

После выходной задержки сигнал может быть инвертирован с помощью преобразования «дополнение до двух», что позволяет положительным и отрицательным выходам ЦАП меняться местами с помощью установки поля DAC\_COMPLEMENT регистра MULTIDUC\_CFG1.

#### Датчик температуры

В состав DAC38RFxx входит блок датчика температуры, который следит за температурой кристалла, измеряя падение напряжения на двух транзисторах. Затем полученное значение падения напряжения преобразуется в 8-битное цифровое слово с помощью аналого-цифрового преобразователя последовательного приближения (successive approximation analog to digital converter, SAR ADC). Результат масштабируется, ограничивается и форматируется в дополнительное до двух (twos complement) значение, представляющее температуру в градусах Цельсия.

Выборка управляется сигналами SDEN и SCLK последовательного интерфейса. Если датчик температуры активирован записью «0» в поле TSENSE\_SLEEP регистра SLEEP\_CONFIG, преобразование выполняется каждый раз, когда по последовательному интерфейсу реализуется операция записи или чтения. Данные только считываются и отправляются наружу цифровым блоком, когда данные с датчика температуры считываются в поле ТЕМРДАТА регистра TEMP\_PLLVOLT. Преобразование использует первые восемь периодов сигнала последовательного тактирования в качестве сигнала тактирования выборки и преобразования, преобразованные данные появляются по спадающему фронту восьмого такта SCLK. Затем по нарастающему фронту девятого такта SCLK данные выводятся из микросхемы. Для работы датчика температуры не требуется никаких других тактов, поэтому он остается активным даже в том случае, если микросхема находится в спящем режиме (sleep mode).

Для нормальной работы описанного выше процесса чтение по последовательному порту из регистра TEMP\_PLLVOLT должно выполняться с периодом SCLK не менее 1 мкс. Если это условие не удовлетворяется, точность датчика температуры значительно уменьшается.

Рис. 11. Управление 50-Ом нагрузкой

#### Наблюдение за сигналами аварийных состояний

Микросхемы DAC38RFxx имеют гибкую систему наблюдения за сигналами аварийных состояний, которую можно использовать для предупреждения о возможности возникновения неисправности. Доступ ко всем флагам аварийных ситуаций предусмотрен с помощью SIP-регистров и/или посредством выводов ALARM сигнализации об аварийных состояниях. После установки сигнала аварийной ситуации соответствующий флаг аварийного состояния должен быть сброшен через последовательный интерфейс, чтобы разрешить дальнейшее тестирование.

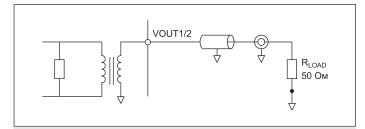

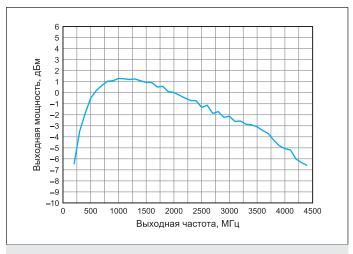

#### Функция преобразования ЦАП

Микросхемы DAC38RFxx имеют внутренний широкополосный согласующий трансформатор (balun) с номинальным частотным диапазоном 0,7–3,8 ГГц для преобразования дифференциального сигнала с ядра ЦАП в несимметричный выходной сигнал. Несимметричный выход используется для работы на 50-Ом нагрузку (рис. 11). При размахе выходного тока в 40 мА теоретическая выходная мощность, отдаваемая в 50-Ом нагрузку, составляет +4 дБм. Однако реальная выходная мощность всегда меньше теоретически возможной. На рис. 12 приведена зависимость выходной мощности от частоты.

Рис. 12. Зависимость выходной мощности от частоты

#### Заключение

Компания Texas Instruments является одним из ведущих производителей микросхем сверхвысокоскоростных ЦАП, работающих в гигагерцевом диапазоне преобразования. Новое семейство ЦАП DAC38RFxx обеспечивает не только большую скорость преобразования, но и хорошие динамические характеристики при высокой степени интеграции и широком наборе функций.

#### Литература

DAC38RFxx Dual-Channel, Single-Ended, 14-Bit, 6- and 9-GSPS, RF-Sampling DAC With JESD204B Interface and On-Chip GSM PLL. www.ti.com/lit/pdf/SLASEF4