| ЦОС | 17

# Новые процессоры

### семейства Blackfin

Одной из основных и наиболее массовых областей применения цифровых сигнальных процессоров (ЦСП) являются так называемые встраиваемые мультимедийные системы — мобильные телефоны, МРЗ-плееры, цифровые камеры, системы IP-телефонии и т. д. Обработка данных в подобных устройствах, как правило, включает в себя два аспекта — интенсивные математические вычисления, характерные для алгоритмов цифровой обработки сигналов, и операции управления, связанные с организацией пользовательского интерфейса, управления потоками данных, поддержкой операционной системы.

Александр СОТНИКОВ

рхитектура классических ЦСП, оптимизированных для максимально эффективного выполнения операций умножения с накоплением, слабо подходит для решения задач второго класса, более характерных для микроконтроллеров и микропроцессоров общего назначения. До недавнего времени для создания встраиваемых мультимедийных систем разработчикам приходилось использовать два отдельных процессора или гетерогенный процессор с интегрированными в одном кристалле ядрами ЦСП и контроллера. Подобная организация обработки данных имеет ряд существенных нелостатков, связанных со сложностью распределения задач между ядрами или дискретными процессорами, увеличением количества корпусов на печатной плате при построении системы на дискретных процессорах, необходимостью использовать два различных набора средств программирования и т. д. Для решения этой проблемы компанией Analog Devices совместно с компанией Intel была разработана архитектура MSA (Micro Signal Architecture, микросигнальная архитектура), совмещающая в себе достоинства 16-разрядного ЦСП и 32-разрядного микроконтроллера и одинаково эффективная как в задачах цифровой обработки сигналов, так и в задачах управления. Процессоры семейства Blackfin, основанные на архитектуре MSA, компания Analog Devices называет «конвергентными», подчеркивая слияние свойств двух типов процессоров в унифицированной архитектуре с единым набором команд.

За прошедшие 7 лет с момента выпуска процессора ADSP-BF535 процессоры Blackfin первого поколения успели прибрести большую популярность как у зарубежных, так и у отечественных разработчиков, благодаря хорошему сочетанию производительности, потребляемой мощности и, что немало-

важно, цены. Продолжая развивать направление конвергентных процессоров, компания Analog Devices анонсировала серийный выпуск в 2008 году двух семейств процессоров Blackfin второго поколения — ADSP-BF54х и ADSP-BF52х. В этой статье дается обзор архитектуры и функциональных возможностей первого из перечисленных семейств, а также основных отличительных черт процессоров ADSP-BF52х(C).

#### Архитектура ядра и памяти ADSP BF54x

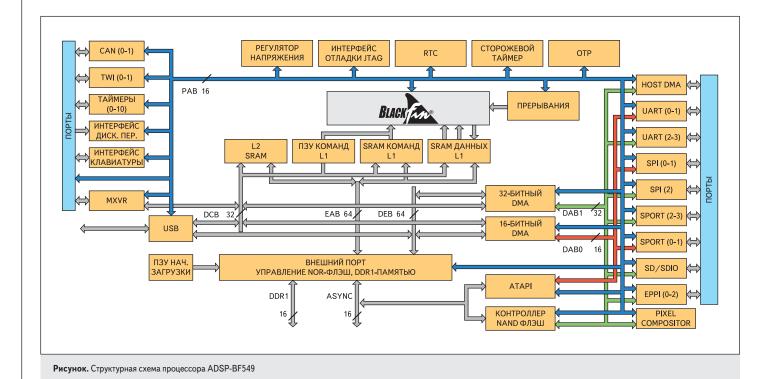

Процессоры ADSP-BF54х представляют собой семейство совместимых программно и по выводам (за исключением процессора ADSP-BF549) 16-разрядных процессоров с фиксированной точкой, которые различаются набором периферийных модулей и производительностью ядра. Структурная схема процессора семейства ADSP-BF54х (а именно, ADSP-BF549) приведена на рисунке.

В основе и ADSP-BF54x, и ADSP-BF52x лежит уже знакомое разработчикам, работавшим с одноядерными или двуядерными процессорами первого поколения, ядро Blackfin. Оно включает в себя вычислительный блок. обеспечивающий арифметические и логические манипуляции над целыми числами, а также над дробными числами в формате с фиксированной точкой, блок формирования адреса, вырабатывающий адреса данных, программный автомат, управляющий процессом выполнения программы, и два регистровых файла — регистровый файл данных (R0-R7) и регистровый файл указателей (P0-P5, FP, SP). Более детальное описание структуры ядра процессоров Blackfin можно найти в публикациях [1, 2]. Максимальная тактовая частота ядра ADSP-BF54x составляет 600 МГц. Сигнал тактовой частоты ядра (ССLК) формируется после повышения частоты внешнего опорного сигнала в интегрированной схеме фазовой автоподстройки частоты (ФАПЧ).

Вся доступная процессору внутренняя и внешняя память, а также регистры интегрированных периферийных модулей отображаются в едином унифицированном адресном пространстве с 32-разрядной адресацией. Процессор поддерживает модифицированную гарвардскую архитектуру с иерархической системой памяти.

Внутренняя память первого уровня (L1) расположена ближе к ядру, работает с частотой ССЬК и разбита на несколько блоков:

- 64 кбайт SRAM памяти команд, из которых 16 кбайт могут быть сконфигурированы как кэш команд;

- 64 кбайт SRAM памяти данных, из которых 32 кбайт могут быть сконфигурированы как кэш данных;

- 4 кбайт SRAM scratchpad-памяти данных;

- 64 кбайт ПЗУ команд.

Области SRAM команд и данных L1, в свою очередь, разбиты на несколько суббанков, имеющих раздельные порты для обращений ядра и обращений контроллера DMA, за счет чего повышается общая производительность системы памяти.

В некоторых процессорах семейства ADSP-BF54х имеется также более медленная внутренняя память второго уровня (L2) объемом 64 или 128 кбайт, которая доступна только как SRAM и может использоваться для хранения и команд, и данных.

Третий уровень иерархии (L3) составляют внутреннее загрузочное ПЗУ и внешняя память, обращение к которым производится через модуль интерфейса внешней шины (EBIU, External Bus Interface Unit). EBIU позволяет процессорам напрямую взаимодействовать с 16-разрядной DDR, SRAM, EPROM и традиционной NOR флэш-памятью, а так-

же буферами FIFO и внешними периферийными модулями, отображаемыми в прост-

ранстве памяти процессора.

Помимо перечисленных областей, отображаемых в карте памяти, процессоры второго поколения имеют небольшой массив внутренней энергонезависимой однократно программируемой (OTP, One-time programmable) памяти объемом 64 кбит, которая используется, в первую очередь, для защиты интеллектуальной собственности. Эта память не является частью линейного пространства памяти процессора, и доступ к ней осуществляется через специальные регистры. Часть ОТР-памяти недоступна для записи и содержит уникальный идентификатор микросхемы и различные служебные данные, запрограммированные при производстве. Оставшаяся часть ОТР-памяти разделена на закрытую (private), которая доступна только в специальном защищенном режиме, и открытую (public), доступ к которой не ограничен.

### Периферия ADSP-BF54x

Как показано на рисунке, процессоры ADSP-BF54х обладают богатым набором интегрированных периферийных модулей. Ряд периферийных модулей, таких как асинхронный (UART) и синхронный (SPORT) последовательные порты, порты SPI, CAN и TWI, часы реального времени (RTC), сторожевой таймер и таймеры общего назначения, присутствовали и в процессорах Blackfin первого поколения и являются стандартными для большинства современных ЦСП. В процессорах Blackfin второго поколения к ним до-

бавилось несколько новых модулей для организации интерфейса с пользователем, другими процессорами и разнообразными устройствами хранения информации, которые ориентированы на создание на базе процессора полнофункциональной мультимедийной системы.

Контроллер USB On-The-Go Dual-Role Device (USBDRC) обеспечивает соединение таких устройств, как сотовые телефоны, цифровые фотокамеры и МРЗ-плееры, с помощью интерфейса USB по принципу «точка-точка» без участия персонального компьютера. Модуль USBDRC может работать в традиционном режиме устройства USB (peripheral-mode), а также в режиме хоста в соответствии с дополнением ОТG к спецификации USB 2.0. В обоих режимах контроллер поддерживает скорость 480 Мбит/с.

Интерфейс клавиатуры представляет собой 16-выводный интерфейсный модуль, предназначенный для детектирования нажатия клавиш на клавиатуре размером до 8×8 элементов. Интерфейс поддерживает фильтрацию дребезга контактов, распознавание одновременного нажатия нескольких клавиш, работу в режиме последовательного нажатия клавиш и нажатия с удерживанием.

Интерфейс вращающихся переключателей — это 32-битный счетчик, позволяющий считывать двухбитные квадратурные или бинарные коды, формируемые промышленными приводами или вращающимися переключателями наподобие ручек регулирования громкости в аудиосистемах.

Для подключения дополнительных внешних устройств хранения данных в процессорах Blackfin второго поколения появились три новых модуля:

- контроллер SD/SDIO для работы с картами памяти и устройствами ввода/вывода, поддерживающими этот интерфейс передачи данных;

- контроллер ATA/ATAPI для подключения CD/DVD и HDD приводов, а также карт памяти CompactFlash в режиме True IDE;

- контроллер NAND флэш-памяти.

Первый модуль имеет выделенные интерфейсные линии, а два других используют тот же набор выводов, что и интерфейс асинхронной памяти ЕВІU, и подразумевают подключение устройств хранения данных к внешней шине процессора. Арбитраж между ЕВІU и контроллерами АТАРІ и NAND осуществляет модуль управления выводами асинхронной памяти (АСМР).

Порт DMA хост-процессора (HOSTDP) позволяет внешнему управляющему процессору обращаться в режиме DMA к внутренней или внешней памяти процессора Blackfin по 8- или 16-разрядной шине данных.

Контроллер уровня МАС мультимедийного трансивера (MXVR), имеющийся только в процессорах ADSP-BF549, предназначен для подключения процессора к сети MOST, широко применяемой в автомобильных мультимедийных системах.

Поскольку наиболее ресурсоемкой операцией в мультимедийных системах является обработка видеоизображений, в состав процессоров Blackfin был включен периферийный модуль для аппаратного ускорения ряда типичных задач обработки видеопикселей — Pixel Compositor. Он работает с входными потоками в формате YUV или RGB и может выполнять смешивание двух цифровых потоков изображения, преобразование цветовых пространств, а также форматирование выход-

Таблица. Периферийные модули процессоров ADSP-BF54x

| Модель     | Количество<br>выводов GPIO | Таймеры | UART | SPORT | EPPI | SPI | TWI | MXVR | CAN | Хост-порт | SDIO | USB  | ATAPI |

|------------|----------------------------|---------|------|-------|------|-----|-----|------|-----|-----------|------|------|-------|

| ADSP BF542 | до 152                     | 8       | 3    | 3     | 1    | 2   | 1   | нет  | 1   | нет       | есть | есть | есть  |

| ADSP BF544 | до 152                     | 11      | 3    | 3     | 2    | 2   | 2   | нет  | 2   | есть      | нет  | нет  | нет   |

| ADSP BF547 | до 152                     | 8       | 4    | 4     | 2    | 3   | 2   | нет  | 0   | есть      | есть | есть | есть  |

| ADSP BF548 | до 152                     | 8       | 4    | 4     | 2    | 3   | 2   | нет  | 2   | есть      | есть | есть | есть  |

| ADSP BF549 | до 152                     | 8       | 4    | 4     | 2    | 3   | 2   | есть | 2   | есть      | есть | есть | есть  |

ного сигнала для отображения на ТFT ЖКдисплее или вывода на цифровой видеокодер стандарта NTSC или PAL.

И, наконец, 16- и 18-разрядные порты ЕРРІ (параллельный периферийный интерфейс с расширенными возможностями) обеспечивают непосредственное подключение к процессору активных ТҒТ ЖК-дисплеев, параллельных АЦП и ЦАП, видеокодеров и декодеров, модулей сенсоров изображения, а также многих других внешних периферийных модулей с параллельным интерфейсом.

Тактирование логики всех периферийных модулей и внешней шины процессора (за исключением модуля RTC, который тактируется внешним кристаллом) осуществляется тактовым сигналом системы, SCLK, который, как и тактовый сигнал ядра, формируется схемой ФАПЧ. Максимально допустимое значение частоты SCLK у процессоров ADSP-BF54x составляет 133 МГц.

Поскольку количество интегрированных периферийных модулей процессора велико, и многие из них в конкретном приложении могут не понадобиться, для уменьшения числа выводов на корпусе множество сигналов периферийных модулей мультиплексируется на ограниченное число внешних линий ввода/вывода общего назначения (GPIO). По умолчанию после сброса все эти выводы работают в режиме GPIO, а альтернативная функция конкретного вывода, соответствующая одному из периферийных модулей процессора, может быть активирована записью в определенный регистр.

Число тех или иных периферийных модулей в процессоре варьируется в зависимости от его модели. Список доступных комбинаций для процессоров ADSP-BF54х приведен в таблипе.

Для снижения нагрузки на ядро процессора пересылки потоков данных между областями памяти и интегрированными периферийными модулями, как правило, осуществляются не путем записи-чтения регистров периферийных узлов ядром, а при помощи четырех контроллеров DMA. Два из них являются выделенными и обеспечивают функционирование наиболее высокоскоростных интерфейсов — контроллера MXVR и контроллера USBDRC. Оставшиеся два контроллера DMA работают с остальными периферийными модулями, поддерживающими прямой доступ к памяти: 32-разрядный контроллер DMAC1 взаимодействует, в основном, с высокоскоростными интерфейсами, а 16-разрядный DMAC0 — с более медленными последовательными портами UART, SPI и SPORT. При этом оба контроллера могут работать с EBIU и имеют по два канала для организации пересылок типа «память-память» между различными областями памяти процессора.

## Дополнительные функциональные возможности

#### Защита программного обеспечения

Одним из наиболее интересных свойств процессоров Blackfin второго поколения является технология защиты программного обеспечения Lockbox, которая представляет собой комплекс аппаратных и программных средств, предназначенных для защиты целостности и конфиденциальности кода и данных.

Аппаратная составляющая технологии Lockbox включает в себя:

- ОТР-память, которая предназначена для хранения открытых и закрытых ключей, и, кроме того, содержит уникальный код микросхемы, запрограммированный при производстве и защищенный от стирания;

- механизмы защиты от несанкционированного доступа (ключи защищенной системы), включая возможность запрета обращений DMA к внутренней памяти и реакций на команды, поступающие от интерфейса отладки JTAG;

- программное обеспечение в ПЗУ команд L1, включающее криптографические алгоритмы и ряд функций для работы с ОТРпамятью;

- аппаратную поддержку защищенных режимов функционирования.

#### Пониженное энергопотребление

В связи с широким применением ЦСП в портативных устройствах с аккумуляторным питанием (сотовых телефонах, СD-плеерах, МР3-плеерах) одной из ключевых характеристик современных ЦСП является потребляемая мощность. Снижение энергопотребления в процессорах Blackfin второго поколения достигается несколькими способами. Во-первых, пользователь имеет возможность варьировать частоты функционирования ядра (CCLK) и системной шины (SCLK) в процессе работы процессора при помощи регистров управления схемы ФАПЧ. Во-вторых, процессор имеет интегрированный регулятор напряжения, который представляет собой контроллер импульсного стабилизатора напряжения, способный формировать уров-

ни напряжения питания ядра из внешнего напряжения в диапазоне от 2,5 до 3,6 В и требующий для функционирования подключения внешнего транзистора, индуктивности и нескольких фильтрующих конденсаторов. С помощью этого регулятора пользователь также может динамически изменять напряжение питания ядра. В третьих, наличие двух независимых доменов тактовых сигналов (домен тактирования ядра и домен тактирования периферии) и нескольких доменов системы питания (домен питания внутренней логики, домен питания контроллера DDR, домен питания контроллера USB, домены питания контроллера MXVR, домен питания RTC и домен питания остальной периферии) позволяет реализовать в BF-54х несколько режимов пониженного энергопотребления, которые характеризуются следующими возможностями:

- отключение только тактового сигнала ядра:

- отключение тактовых сигналов ядра и синхронной части периферии (за исключением часов реального времени);

- отключение тактовых сигналов ядра и периферии, а также прекращение подачи напряжения на ядро процессора (при использовании внутреннего регулятора).

# Особенности процессоров ADSP-BF52x(C)

Основная цель, которая преследовалась при разработке процессоров семейства ADSP-BF52x, заключается в обеспечении наилучшего соотношения цены и производительности. Представители этого семейства превосходят по характеристикам старшие из одноядерных процессоров Blackfin первого поколения, но имеют ряд упрощений по сравнению с более дорогими процессорами ADSP-BF54x. Во-первых, в них используется упрощенная схема организации DMA с одним 16-разрядным контроллером. Во-вторых, в процессорах ADSP-BF52х нет внутренней памяти второго уровня. В наборе периферии отсутствуют интерфейсы ATAPI, SDIO и модуля Pixel Compositor, а в некоторых моделях есть контроллер MAC Ethernet 10/100. Кроме того, в них сокращено общее количество выводов GPIO (48 вместо 152). Вместо контроллера DDR-памяти в ADSP-BF52x, как и в процессорах первого поколения, используется контроллер SDRAM. И, наконец, подсемейство процессоров с суффиксом С, которые ориентированы на применение в портативных аудиоустройствах наподобие CD- и MP3-плееров, отличается наличием на кристалле интегрированного стереокодека.

Процессоры ADSP-BF52х выпускаются в двух версиях — стандартной и с пониженным энергопотреблением. Они производятся по разным технологическим процессам, имеют разные допустимые тактовые частоты ядра (600 и 400 МГц соответственно) и системной шины (133 и 80 МГц соответственно).

Стандартные версии процессоров имеют нечетные, а версии с пониженным энергопотреблением — четные порядковые номера. Так, например, процессор ADSP-BF522 представляет собой малопотребляющий вариант процессора ADSP-BF523.

#### Заключение

Высокая производительность, богатая периферия, низкое энергопотребление и расширен-

ные возможности по защите интеллектуальной собственности делают процессоры Blackfin второго поколения идеальной платформой для создания самых разнообразных устройств обработки сигналов и изображений. Широкий спектр моделей, обладающих программной совместимостью и совместимостью по выводам (в пределах отдельно взятого семейства), с различными комбинациями цены, производительности и набора периферийных модулей позволяет разработчику выбрать процессор,

который наилучшим образом подходит для решения стоящей перед ним задачи.

### Литература

- 1. Сотников А. Особенности архитектуры и программирования двуядерных процессоров семейства Blackfin ADSP-BF561 // Компоненты и технологии. 2007. № 6.

- 2. Новые разработки DSP: семейство Blackfin // Цифровая обработка сигналов. 2001. № 4.